# RDA012RZ

12 Bit 1.0 GS/s Return to Zero DAC

REV-DATE PB3-2412 FILE DS\_0022PB3-2412

# RDA012RZ

# 12 Bit 1.0 GS/s Return to Zero DAC

#### **Features**

- ♦ 12 Bit Resolution

- 1 GS/s Minimum Sampling Rate

1.5 GS/s Typical

- ♦ 10 Bit Static Linearity

- ♦ LVDS Compliant Digital Inputs

- ♦ Power Supply: -5.2V, +3.3V

- ♦ Input Code Format: Offset Binary

- ♦ Output Swing: 600 mV @ 50 Ω Termination

- Reference I/O Pin for Accurate Full-Scale Adjustment

- Return-to-Zero Output for 2nd Nyquist Operation

- ♦ Differential ECL or Sinusoidal Clock Input

- Fast settling time: < 1ns 0.1% (+/- 2LSB), switching from code 1536 to 2560 (quarter scale)

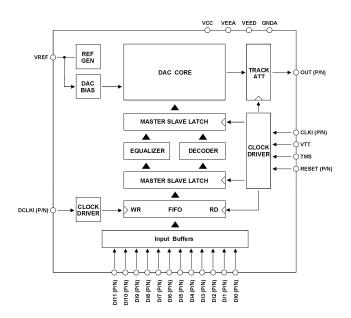

Figure 1. Functional Block Diagram

## **Product Description**

The RDA012RZ is a 12-bit GaAs DAC with a data update rate over 1Gsample/s. It has been optimized for ultra-high speed applications. The DAC utilizes a segmented current source to

reduce the glitch energy and to achieve high linearity performance. For a flat response at the second Nyquist analog band, a track-and-attenuate circuit is integrated.

### Ordering information

| PART NUMBER   | DESCRIPTION                     | CAUTION                 | <b>A</b> |

|---------------|---------------------------------|-------------------------|----------|

| RDA012RZ-QP   | 12 BIT 1GS/s RZDAC, QFP Package | DEVICE SUSCEPTIBLE TO   |          |

| RDA012RZ-DI   | 12 BIT 1GS/s RZDAC, DIE         | DAMAGE BY ELECTROSTATIC | A SA     |

| EVRDA012RZ-QP | RDA012RZ-QP Evaluation Board    | DISCHARGE (ESD)         | 100      |

# Absolute Maximum Ratings

| Supply Voltages  VEEA, VEED to GNDA  VCC to GNDA |              |

|--------------------------------------------------|--------------|

| RF Input Voltages                                |              |

| CLKI to GNDA                                     | 0 V to VCCD  |

| HS Digital Input Voltages                        |              |

| DI<11:0>                                         | 0 V to VCCD  |

| DCLK                                             |              |

| RESET                                            |              |

| Temperature                                      |              |

| Case Temperature                                 | 40 to +85 °C |

| Junction Temperature                             | +125 °C      |

| Lead, Soldering (10 Seconds)                     |              |

| Storage                                          | 60 to 125 °C |

# **DC Electrical Specification**

Test Conditions (see notes for specific conditions): Room Temperature; VCC = 3.3V; VEEA = -5.2V; VEED = -5.2V; VREF = -2V; VTT = -2V; TMS = RZ Mode; Clock: 1GHz, 0.6Vpp Differential; Outputs Terminated Into 50  $\Omega$  to VCC.

|     | PARAMETER                     | SYMBOL             | CONDITIONS, NOTE                                               | MIN  | TYP  | MAX  | UNITS |

|-----|-------------------------------|--------------------|----------------------------------------------------------------|------|------|------|-------|

| 1.0 | DC TRANSFER FUNCTION          |                    |                                                                | •    | •    |      |       |

| 1.1 | Differential Nonlinearity     | DNL                |                                                                | -0.1 |      | 0.1  | %FS   |

| 1.2 | Integral Nonlinearity         | INL                |                                                                | -0.1 |      | 0.1  | %FS   |

| 2.0 | TEMPERATURE DRIFT             |                    |                                                                |      |      |      |       |

| 2.1 | Warm-up Time                  |                    | After Power-up                                                 |      |      | 30   | S     |

| 3.0 | <b>CLOCK INPUT (CLKIP, CL</b> | KIN)               |                                                                |      |      |      |       |

| 3.1 | Input Resistance              | R <sub>CLKI</sub>  | Resistance (CLKI P/N) to VTT                                   | 45   | 50   | 55   | Ω     |

| 4.0 | DATA CLOCK INPUTS (DC         | LKIP, DCI          |                                                                |      |      |      |       |

| 4.1 | Input Resistance              | R <sub>DCLKI</sub> | Between P/N Input Pair                                         | 90   | 100  | 110  | Ω     |

| 4.2 | Input Capacitance             | C <sub>DCLKI</sub> | On Each Input, Single Ended                                    |      | 2    |      | pF    |

| 5.0 | DIGITAL INPUTS (DI<0:11)      | P, DI<0:1          | 1>N)                                                           |      |      |      |       |

| 5.1 | Input Resistance              | $R_{DIN}$          | Between P/N Input Pair                                         | 90   | 100  | 110  | Ω     |

| 5.2 | Input Capacitance             | $C_{DIN}$          | On Each Input, Single Ended                                    |      | 2    |      | pF    |

| 6.0 | ANALOG OUTPUTS (OUTP          | P, OUTN)           |                                                                |      |      |      |       |

| 6.1 | Full-scale Output Swing       | $V_{FSD}$          | Differential, Terminated Into $50\Omega$ to GND on Each Output | 1140 | 1200 | 1260 | mVpp  |

| 6.2 | Full-scale Output Swing       | V <sub>FSS</sub>   | Single Ended, Terminated Into $50\Omega$ to GND                | 570  | 600  | 630  | mVpp  |

| 6.3 | Full-scale Output Range       | V <sub>FSRS</sub>  | Single Ended, Terminated Into 50Ω to GND (MIN=000h, MAX=FFFh)  | -630 |      | 0    | V     |

| 6.4 | Output Current                | I <sub>OUT</sub>   | Terminated Into 50Ω to GND                                     | 11.4 | 12   | 12.6 | mΑ    |

| 7.0 | REFERENCE (VREF)              |                    |                                                                |      |      |      |       |

| 7.1 | Reference Voltage             | $V_{VREF}$         |                                                                |      | -2   |      | V     |

| 8.0 | POWER SUPPLY REQUIRE          | EMENTS             |                                                                |      |      | •    |       |

| 8.1 | Positive Current              | ICC                |                                                                |      | 45   |      | mΑ    |

| 8.2 | Negative Current, Analog      | IEEA               |                                                                |      | 120  |      | mΑ    |

| 8.3 | Negative Current, Digital     | IEED               |                                                                |      | 400  |      | mΑ    |

| 8.4 | Power Dissipation             | Р                  |                                                                |      | 2.8  | 3.1  | W     |

# **AC Electrical Specification**

Test Conditions (see notes for specific conditions): Room Temperature; VCC = 3.3V; VEEA = -5.2V; VEED = -5.2V; VREF = -2V; VTT = -2V; TMS = RZ Mode; Clock: 1GHz, 0.6Vpp Differential; Outputs Terminated Into 50  $\Omega$  to VCC.

|     | PARAMETER             | SYMBOL | CONDITIONS, NOTE                         | MIN | TYP | MAX | UNITS |

|-----|-----------------------|--------|------------------------------------------|-----|-----|-----|-------|

| 9.0 | DYNAMIC PERFORMANCE   |        |                                          |     |     |     |       |

| 9.1 |                       | SFDR1  | $F_{clk} = 1000MHz$ , $F_{out} = 550MHz$ | 50  |     |     | dBc   |

| 9.2 | Spurious Free Dynamic | SFDR2  | $F_{clk} = 1000MHz$ , $F_{out} = 667MHz$ | 50  |     |     | dBc   |

| 9.3 | Range                 | SFDR3  | $F_{clk} = 1000MHz$ , $F_{out} = 750MHz$ | 50  |     |     | dBc   |

| 9.4 |                       | SFDR4  | $F_{clk} = 1000MHz$ , $F_{out} = 950MHz$ | 50  |     |     | dBc   |

| 9.5 | Clock Feedthrough     | FD     | $F_{clk} = 1000MHz$                      |     |     | -40 | dB    |

| 9.6 | Output Flatness       | ATT    | Attenuation at F <sub>out</sub> = 950MHz |     |     | 6   | dB    |

# **Operating Conditions**

|      | PARAMETER                   | SYMBOL                 | CONDITIONS, NOTE             | MIN   | TYP  | MAX   | UNITS |  |

|------|-----------------------------|------------------------|------------------------------|-------|------|-------|-------|--|

| 10.0 | CLOCK INPUTS (CLKIP, CLKIN) |                        |                              |       |      |       |       |  |

| 10.1 | Amplitude                   | V <sub>CPP,HCLKI</sub> | Differential                 | 400   | 600  | 800   | mV    |  |

| 10.2 | Common Mode Voltage         | $V_{\text{CCM,HCLKI}}$ |                              | -2    | -1.5 | -0.8  | V     |  |

| 10.3 | Maximum Frequency           | F <sub>MAX,HCLKI</sub> |                              | 1     | 1.5  |       | GHz   |  |

| 10.4 | Minimum Frequency           | F <sub>MIN,HCLKI</sub> |                              |       |      | 1     | MHz   |  |

| 11.0 | DATA CLOCK INPUTS (DCL)     | (IP, DCLK              | IN)                          |       |      |       |       |  |

| 11.1 | Amplitude                   | $V_{DPP}$              | Differential                 | 200   |      |       | mV    |  |

| 11.2 | Common Mode Voltage         | $V_{DCM}$              |                              | 0.2   |      | 2.2   | V     |  |

| 12.0 | DIGITAL INPUTS (DI<0:11>P   | , DI<0:11>I            | ,                            |       |      |       |       |  |

| 12.1 | Amplitude                   | $V_{DPP}$              | Differential                 | 200   |      |       | mV    |  |

| 12.2 | Common Mode Voltage         | $V_{DCM}$              |                              | 0.2   |      | 2.2   | V     |  |

| 12.3 | Data In to DCLKI Setup      | t <sub>DTDKST</sub>    | Both Edges of DCLKI          | 100   |      |       | ps    |  |

| 12.4 | Data In to DCLKI Hold       | t <sub>DTDKHD</sub>    | Both Edges of DCLKI          | 100   |      |       | ps    |  |

| 13.0 | TERMINATION VOLTAGE (V      | TT)                    |                              |       |      |       |       |  |

| 13.1 | Reference Voltage           | $V_{TT}$               | Termination Voltage for CLKI |       | -2   |       | V     |  |

| 14.0 | REFERENCE (VREF)            |                        |                              |       |      |       |       |  |

| 14.1 | Reference Voltage           | $V_{REF}$              | External Reference           |       | -2   |       | V     |  |

| 15.0 | POWER SUPPLY REQUIREMENTS   |                        |                              |       |      |       |       |  |

| 15.1 | Positive Supply             | VCC                    |                              | 3.1   | 3.3  | 3.5   | V     |  |

| 15.2 | Negative Supply, Analog     | VEEA                   |                              | -5.45 | -5.2 | -4.75 | V     |  |

| 15.3 | Negative Supply, Digital    | VEED                   |                              | -5.45 | -5.2 | -4.75 | V     |  |

| 16.0 | 0 OPERATING TEMPERATURE     |                        |                              |       |      |       |       |  |

| 16.1 | Case Temperature            | Tc                     | Measured at Bottom Plate     | -40   |      | 85    | °C    |  |

| 16.2 | Junction Temperature        | Tj                     |                              |       |      | 125   | °C    |  |

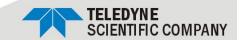

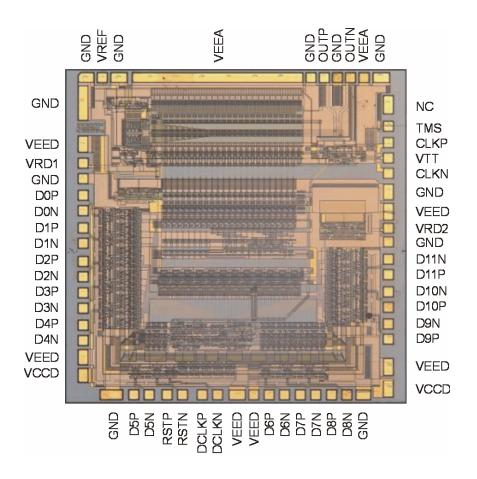

## Pin Description Pin Layout (TOP view)

| P/I/O | PIN                                                | NUM. | NAME        | FUNCTION                                                        |  |

|-------|----------------------------------------------------|------|-------------|-----------------------------------------------------------------|--|

| Р     | 23                                                 | 1    | VCC         | VCC Power Supply                                                |  |

| Р     | 48, 53, 54, 55, 56, 57, 58                         | 7    | VEEA        | Analog VEE Power Supply                                         |  |

| Р     | 2, 15, 24, 32, 41                                  | 5    | VEED        | Digital VEE Power Supply                                        |  |

| Р     | 1, 4, 16, 31, 39, 42, 47, 50, 52, 59, bottom plate | 10   | GND         | Ground                                                          |  |

|       | 3                                                  | 1    | VRD1        | Test Pin: Bypass to Ground                                      |  |

| ı     | 40                                                 | 1    | VRD2        | Test Pin: Bypass to Ground                                      |  |

| ı     | 60                                                 | 1    | VREF        | -2V External Reference Voltage                                  |  |

| ı     | 44                                                 | 1    | VTT         | Clock Termination Voltage                                       |  |

| I     | 46                                                 | 1    | TMS         | Track Mode Select: Float – RZ Function<br>Ground – ZOH Function |  |

| - 1   | 19                                                 | 1    | RESETP      | RESETP / RESETN Is Reset Input                                  |  |

| ı     | 20                                                 | 1    | RESETN      | KLOLIF / KLOLIN is Keset input                                  |  |

| - 1   | 45                                                 | 1    | CLKIP       | CLKIP / CLKIN Is Clock Input                                    |  |

| ı     | 43                                                 | 1    | CLKIN       | CLRIP / CLRIN IS CIOCK INPUL                                    |  |

| I     | 5, 7, 9, 11, 13, 17, 25, 27, 29, 33, 35, 37        | 1    | DI <i>P</i> | DI <i>P / DI<i>N Is Digital Bit I Input. MSB is Bit 11.</i></i> |  |

| I     | 6, 8, 10, 12, 14, 18, 26, 28, 30, 34, 36, 38       | 1    | DI <i>N</i> | DICIPE / DICIPIN IS DIGITAL BILL I III PUL. MISB IS BIL I I .   |  |

| I     | 21                                                 | 1    | DCLKIP      | DCLKIP / DCLKIN Is Data Clock Input                             |  |

| I     | 22                                                 | 1    | DCLKIN      | DOLNIF / DOLNIN IS DAIA Clock Input                             |  |

| 0     | 51                                                 | 1    | OUTP        | OUTP / OUTN Is Differential Output                              |  |

| 0     | 49                                                 | 1    | OUTN        | OOTI / OOTIN IS Dilleterillar Output                            |  |

Figure 2. RDA012RZ-QP pinout (top view).

# Die Plot and Pad Arrangement

Figure 3. RDA012RZ die pad layout.

### Theory of Operation

The DAC employs MSB segmentation, and the number of bits segmented is carefully chosen for the best compromise between static and dynamic linearity. The 12-bit digital data inputs are latched by a master-slave flip-flop immediately after the input buffer to reduce data skew. MSB data bits are decoded into a thermometer code by a two-stage decoding block, and the LSB data bits are transported through the delay equalizer block. The digital data are synchronized again by a second master-slave flip-flop to reduce the switching glitch. The decoded MSB and LSB data bits drive identical current switches. The output nodes from the LSB current switches are connected to the analog output through a R-2R ladder to generate the binary-weighted analog output.

A track-and-attenuator (T/A) circuit is integrated with the DAC, for a wider output bandwidth. A traditional DAC can be modeled as an ideal sampler followed by a zero order hold (ZOH) circuit to the DAC. Due to the sinc(x) (=sin(x)/x) frequency behavior of the ZOH circuit, the DAC output has notches at the frequencies which are multiples of the sampling clock frequency. Also, the DAC's glitch causes unwanted spurious tones when the output frequency of the DAC is high. A track-and-hold amplifier can be used to re-sample the DAC output, mainly to reduce the performance degradation due to the glitch caused by the different switching instances of the DAC current switches. A carefully designed track-and-hold successfully deglitches the DAC output, but the signal drop due to the sinc(x) characteristics still remains. The spectral flatness of the DAC output can be improved by implementing return-to-zero (RZ) DAC. The RZ DAC output can be achieved by adding a track-and-attenuator circuit after the DAC. For an RZ DAC with an output duty cycle of D, the DC output power loss is -20\*log<sub>10</sub>(D), but the output notch happens at

multiples of Fclk/D. For example when the duty cycle is 50% the notch is at 2GHz, 4GHz, etc for a 1GS/s RZ DAC. The T/A circuit add spurs of its own.

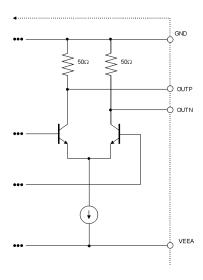

The DAC output full-scale voltage follows the relationship  $V_{FS} = 0.3xV_{REF}$ . An internal reference circuit with approximately 20dB supply rejection is integrated on chip for a convenient application, and a reference pin is provided for monitoring and for bypass purposes. To band-limit the noise on the reference voltage, the reference pin should be bypassed to the GNDA node with capacitance > 100pF. The VREF pin can also be used to override the internal reference with an accurate, temperaturecompensated external voltage reference. Figure 4 shows the equivalent circuit of the DAC output ports. The DAC outputs are terminated internally to GNDA with  $50\Omega$  equivalent resistors, and need an external 50 termination to at the output pin for a full-scale voltage of 600mV with a 2-volt reference voltage.

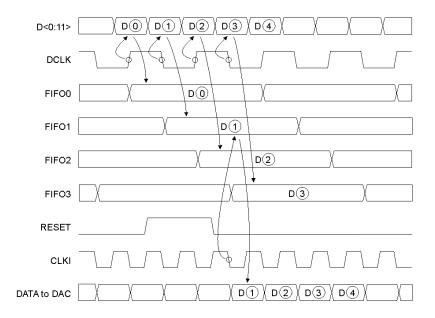

A 4-clock deep FIFO is included to compensate the delay skews in the data and clock line. The incoming digital data is latched on both edges of the DCLK. As a result, for 1Gb/s data stream, the input DCLK will have 500MHz frequency, so that the clock shape will be similar to the data signal except that the DCLK waveform would be shifted by 90°. In other words, the rising and falling edges of the DCLK will happen at the moment that the data signals have the widest windows to latch onto. The read clock of the FIFO will start reading the incoming data after the RESET is set to logic 0.

### Signal Description

#### POWER SUPPLIES

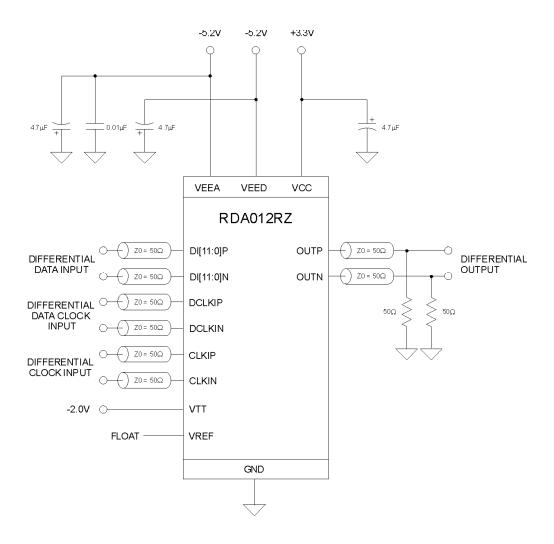

The RDA012RZ has several power supplies. Their names and uses are defined in the pin description section. Different power supply pins are separated inside the chip, and using separate regulators for each supply is recommended for a good isolation between the digital and analog sections of the chip. No power sequencing is required for reliable operation. Also due to the high-breakdown voltage of the device technology, input may be activated upon an unpowered DAC without damaging the part.

#### ANALOG OUTPUT and REFERENCE

The outputs OUTP and OUTN should both be connected though a 50  $\Omega$  resistor to GNDA. This will give a full-scale amplitude of 0.6 volt, 1.2-volt differentially.

VREF pin is provided for an added control over the full-scale of the DAC. The internal reference circuit is designed to provide -2.0 volt with -20dB VEE power supply sensitivity (PSS), which can change up to ±5% as the supply voltage and/or operating temperature changes. If the user prefers accurate absolute fullscale, one can use external voltage reference with low output impedance to override the internal reference. Separate reference pins are provided for the digital reference voltage as well. However the accuracy of the digital reference voltages are not as crucial as the analog reference. A proper bypass circuitry would suffice for the digital reference pins. Note that the DAC is designed for a reference voltage of -2.0 volt. The output resistance of the reference node is 560  $\Omega$  ±10%.

#### INPUT CLOCK

The RDA012RZ clock inputs can be driven from a typical ECL circuits. Also a differential sinusoidal clock can be used to drive the DAC. A differential clock should be provided to the CLKP and CLKN inputs,

which are internally terminated with  $50\Omega$ . The VTT pin is the termination node for both CLKP and CLKN, and should be connected to a well de-coupled -2.0 volt supply. Since the DAC's output phase noise is directly related to the input clock noise and jitter, a low-jitter clock source should be used to drive the clock input. The internal clock driver generates very little added jitter ( $\sim$ 100fs) to the internal clock, and the incoming clock signal's spectral purity needs to be guaranteed to take advantage of the low-noise clock driver circuit inside. A 900MHz DAC output demands a white-noise induced clock jitter of less than 280fs for a 10-bit equivalent, 62dB SNR.

#### DATA INPUT and DCLOCK

According to the LVDS standards, data inputs need to have 100  $\Omega$  terminations between the positive and the complimentary terminals. For convenient application and better performance, the termination resistors are included on the chip.

The data input clock is supplied by the DSP or ASIC that provides the digital data for the DAC. RDA012RZ employs a four (4)-clock deep FIFO to provide a robust interfacing with the digital driver chip. The digital data are written to the FIFO on both edges of the DCLK, and read into the DAC register on each rising edge of the DAC clock (CLKI). A four-clock deep FIFO provides a skew margin of worst-case 1½ full clock cycle in both positive and negative direction. To ensure a robust data interface, RESET pin is provided. The read clock of the FIFO is enabled when RESET signal is low, starts to feed the digital data to the DAC.

A timing example scenario is given in Figure 5. When the RESET signal goes low, the data stored in the register FIFO1 exhibits the widest timing window. So the data D(1) is taken into the F/F from the FIFO. By employing 4 clocks deep FIFO, maximum delay fluctuation of 1.5  $t_{\rm ck}$  between the RCLK and the DCLK can be tolerated.

Figure 4. RDA012RZ equivalent output circuit.

Figure 5. RDA012RZ input data timing.

## **Typical Operating Circuit**

Figure 6. RDA012RZ typical operating circuit using internal voltage reference.

## Typical Performance

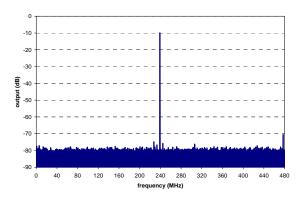

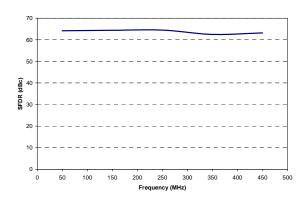

Figure 7.  $1^{st}$  Nyquist output for  $f_{CLK}$ =960MHz,  $f_{OUT}$ =240Mhz

Figure 8. SFDR x f<sub>OUT</sub>, f<sub>CLK</sub>=1GHz 1<sup>st</sup> Nyquist

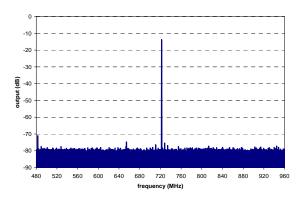

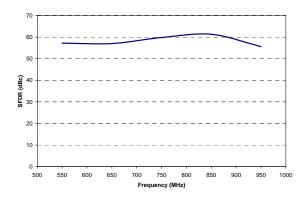

Figure 9. 2<sup>nd</sup> Nyquist output for f<sub>CLK</sub>=960MHz, f<sub>OUT</sub>=720Mhz

Figure 10. SFDR x f<sub>OUT</sub>, f<sub>CLK</sub>=1GHz 2<sup>nd</sup> Nyquist

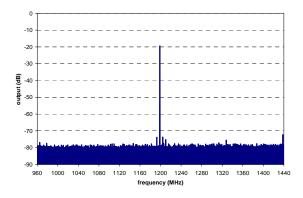

Figure 11. 3<sup>rd</sup> Nyquist output for f<sub>CLK</sub>=960MHz, f<sub>OUT</sub>=1200Mhz

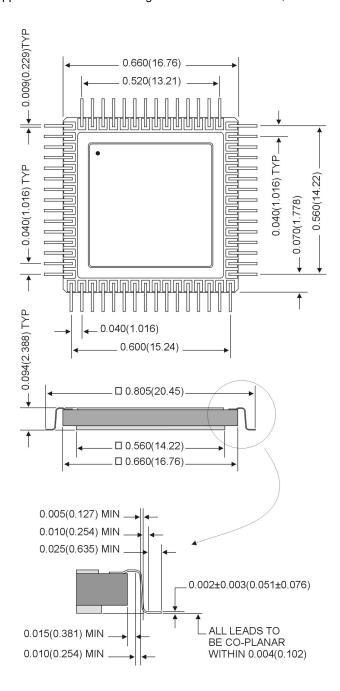

## Package Information

The RDA012RZ is shipped in a 60-pin QFP. The package has a CuW base for heat spreading that should be soldered to copper on a PCB. The Package

body including lid is electrically tied to GND internally. All dimensions are in inches (mm). Tolerances are ±0.005 inches, unless otherwise noted.

Figure 12. RDA012RZ-QP package, Dimensions shown in inches (mm).